特長

システムスロットは、フロント面より右側と左側にコンフュギレーションされた2タイプがあり、スロット数は1〜4、6、8の6種類が用意されております。

全信号ラインは内層に配置されており、特性インピーダンスを65Ωに設定しております。

I/Oバッファ用電源(V I/O)は、+ 5V、+ 3.3Vの供給をシステムに応じて任意に設定できます。

ジオグラフィカルアドレスはバックプレーン上(P2、A22〜E22)でバイナリー設定されております。

INT A、B、C、Dのルーティングは、ほとんどの標準BIOSに対応しております。

従来のPICMG REV1.0のほとんどのCPUボードに対しても動作可能です。

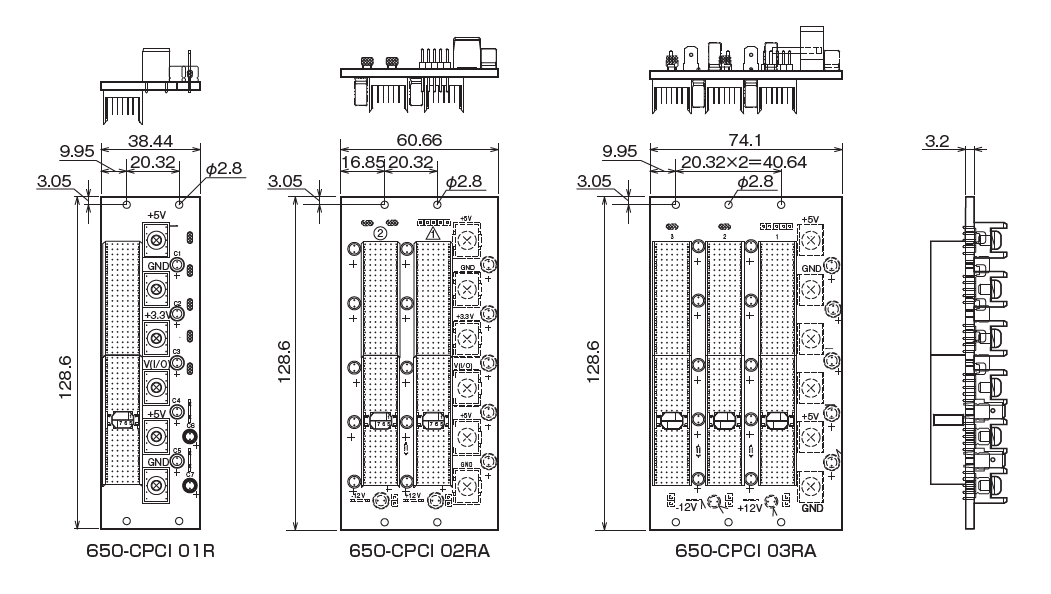

| オーダーコード | L | スロット数 | システムスロット (フロント面より) |

|---|---|---|---|

| 650-CPCI 01R | 38.44 | 1 | – |

| 650-CPCI 02RA | 60.66 | 2 | 右 |

| 650-CPCI 03RA | 74.1 | 3 | 右 |

仕様

基板材質…… FR-4(3.2t)10層

但し、1スロットは、FR-4(3.2t)6層

コネクタ……2㎜HMコネクタ

給電方法…… ネジ止め端子、ファストン端子

+ 5V (MAX 60A)

+ 3.3V (MAX 30A)

V I/O (MAX 30A)

+ 12V (MAX 10A)

− 12V (MAX 10A)

外形寸法図

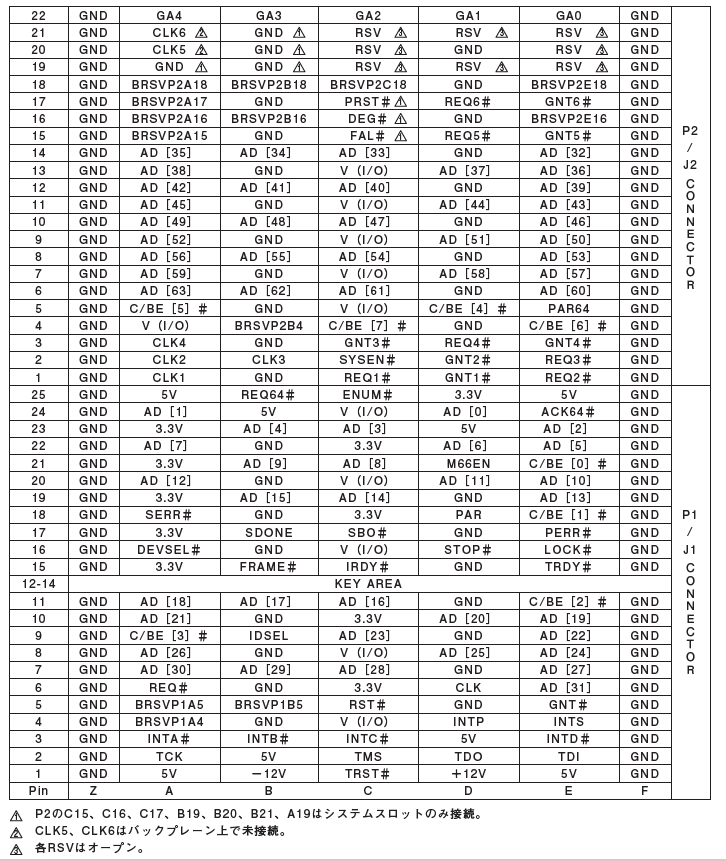

PICMG2.0 REV2.1 バックプレーンピンアサイン表

[PICMG2.0 REV2.1 Specification]より

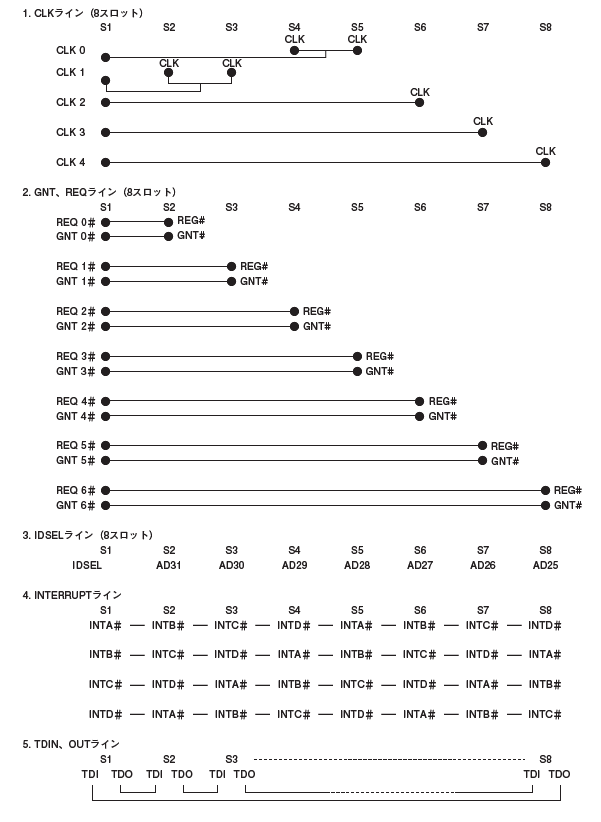

バックプレーンパターン接続仕様

お客様の仕様、サイズに基づく特注品も承ります。

お問い合わせ

フォームが表示されるまでしばらくお待ち下さい。

恐れ入りますが、しばらくお待ちいただいてもフォームが表示されない場合は、こちらまでお問い合わせください。